PDF) Low-power high-speed performance of current-mode logic D flip-flop topology using negative-differential-resistance devices

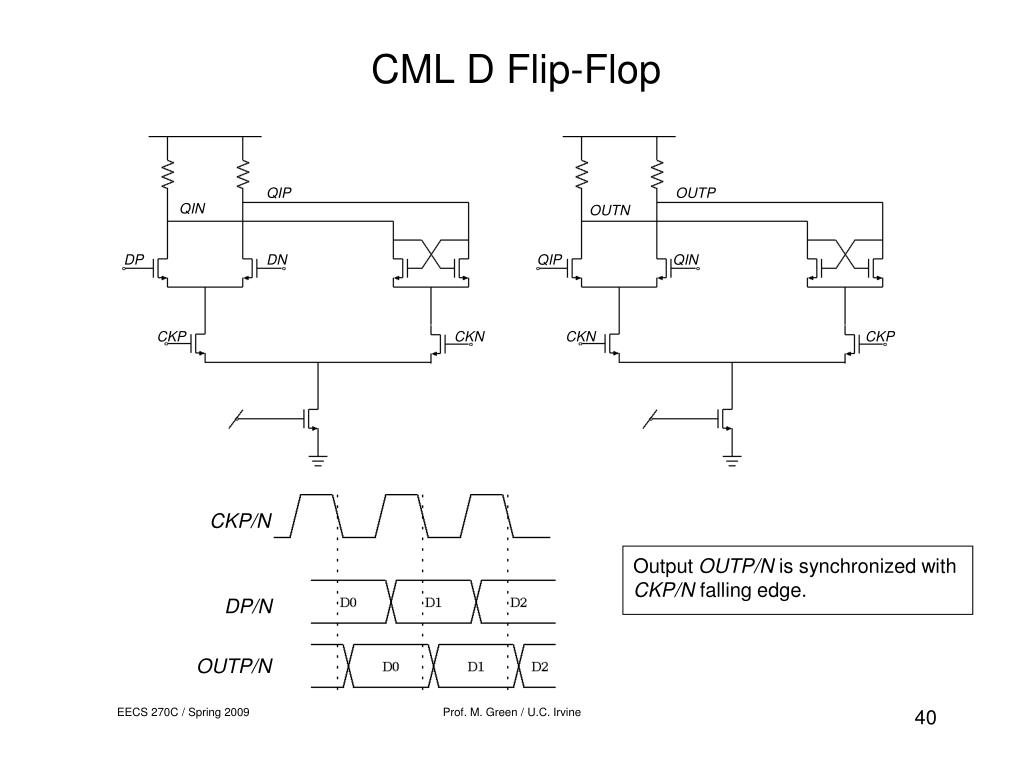

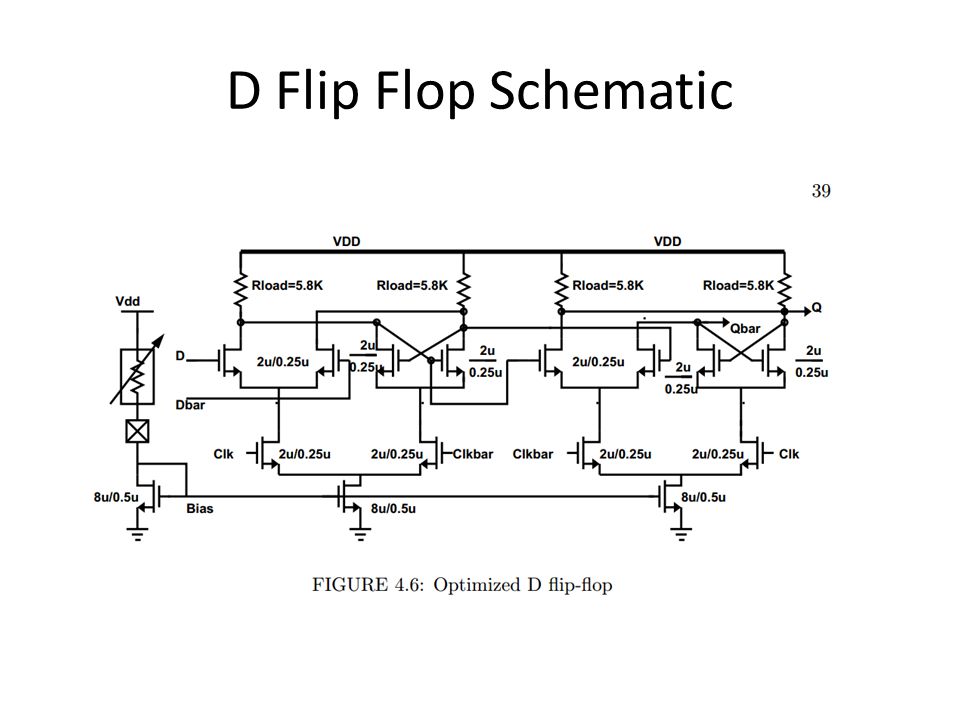

Part 01: Proposal and Overview. Dual Modulus Prescaler Using Current Mode Logic Goals 2.5 GHz Operation 8/9 Dual Modulus 0.18uM BSIM 3 Model. - ppt download

A 2-GHz, Low Noise, Low Power CMOS Frequency Synthesizer with an LC-tuned VCO for Wireless Communications

RTD-based High Speed and Low Power Integrated Circuits RTD-based High Speed and Low Power Integrated Circuits

PDF) Low-power high-speed performance of current-mode logic D flip-flop topology using negative-differential-resistance devices

KR100682266B1 - Differential output tspc d-type flip flop and frequency divider using it - Google Patents