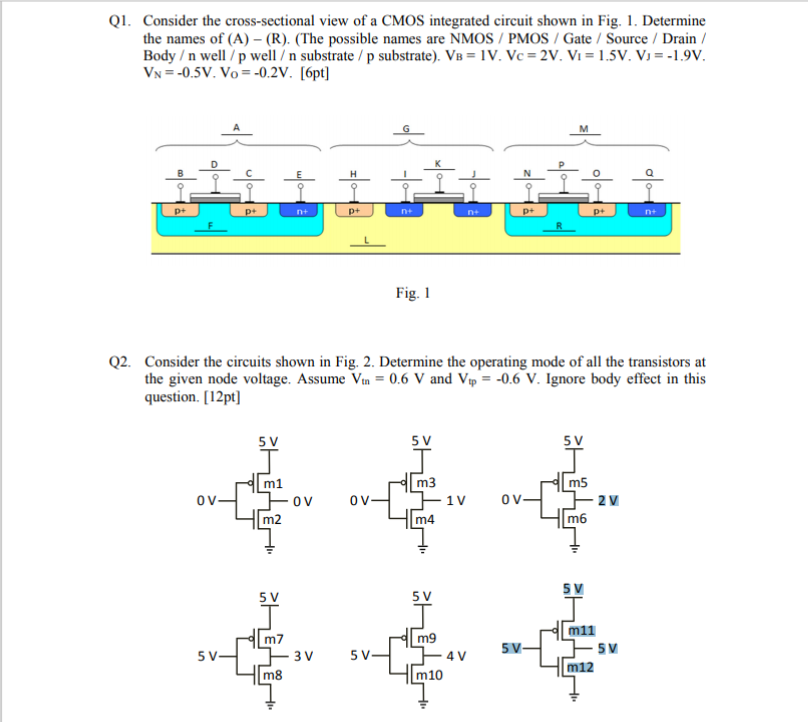

Figure 2 from Fully Depleted Silicon on Insulator Devices CMOS: The 28-nm Node Is the Perfect Technology for Analog, RF, mmW, and Mixed-Signal System-on-Chip Integration | Semantic Scholar

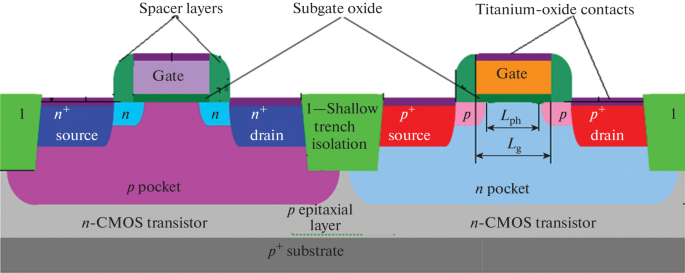

Figure 1 from A 1.8-GHz 33-dBm $P$ 0.1-dB CMOS T/R Switch Using Stacked FETs With Feed-Forward Capacitors in a Floated Well Structure | Semantic Scholar

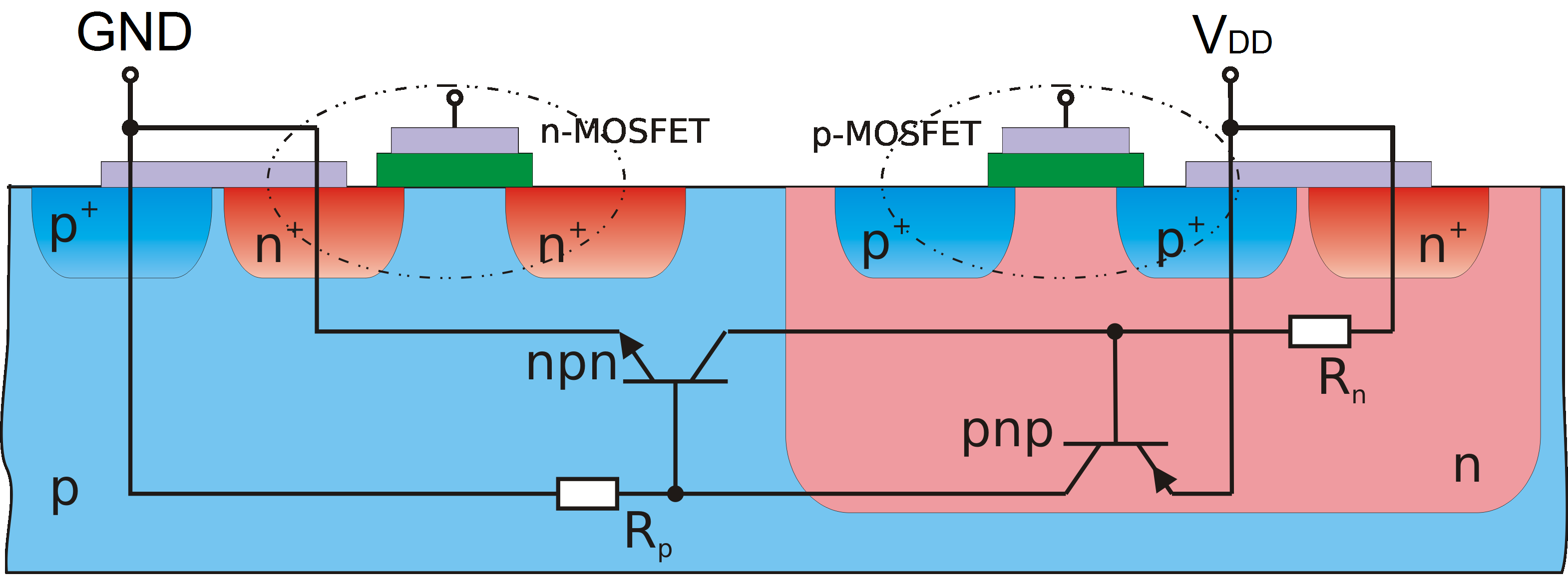

Cross section view of CMOS gates (a) without triple-well and (b) with... | Download Scientific Diagram

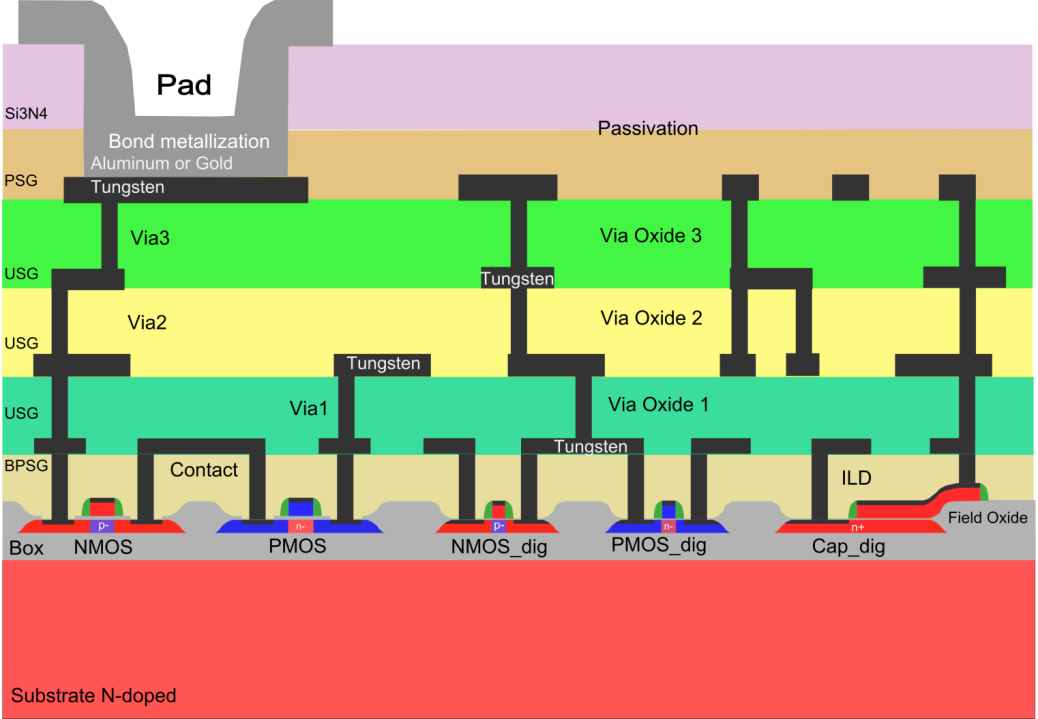

Performance of CMOS pixel sensor prototypes in ams H35 and aH18 technology for the ATLAS ITk upgrade - CERN Document Server

Possibilities and Limitations of CMOS Technology for the Production of Various Microelectronic Systems and Devices | SpringerLink

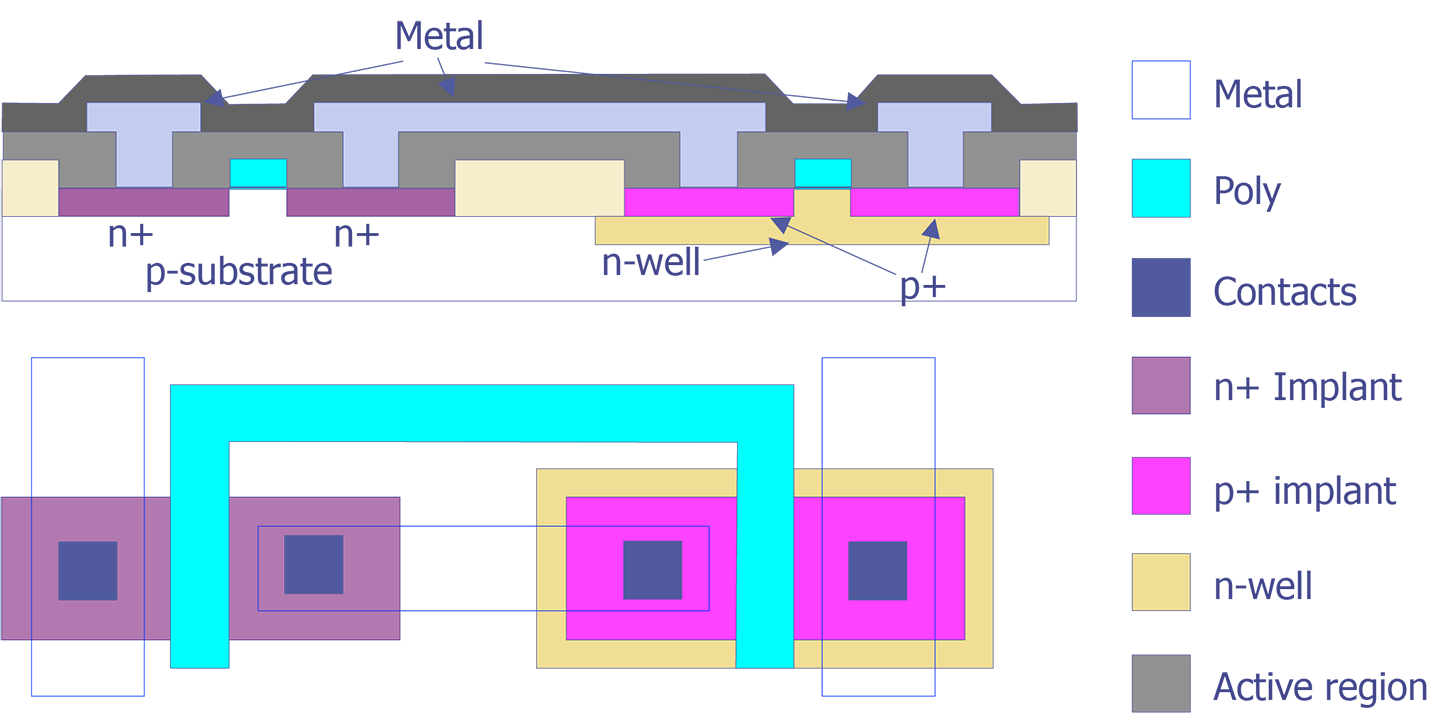

![Simplified cross-sectional view [Wikipedia.org 2010] (a) and layout of... | Download Scientific Diagram Simplified cross-sectional view [Wikipedia.org 2010] (a) and layout of... | Download Scientific Diagram](https://www.researchgate.net/publication/301317714/figure/fig1/AS:428467809460229@1479166094628/Simplified-cross-sectional-view-Wikipediaorg-2010-a-and-layout-of-a-CMOS-inverter.png)

Simplified cross-sectional view [Wikipedia.org 2010] (a) and layout of... | Download Scientific Diagram

Top) Cross-sectional view of a CMOS inverter struck by an ion with a... | Download Scientific Diagram

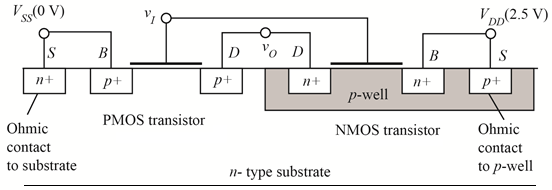

![Solved [16 pts] The figure below shows cross-section diagram | Chegg.com Solved [16 pts] The figure below shows cross-section diagram | Chegg.com](https://media.cheggcdn.com/media%2Fe5a%2Fe5af50e3-cd51-4352-88b7-0cedad5b00a5%2FphpMUSMdS.png)